Product Summary

The XC4005E-4PQ100C is a high-performance, high-capacity Field Programmable Gate Array (FPGA). The XC4005E-4PQ100C provides the benefits of custom CMOS VLSI, while avoiding the initial cost, long development cycle, and inherent risk of a conventional masked gate array. The result of thirteen years of FPGA design experience and feedback from thousands of customers, the XC4005E-4PQ100C combines architectural versatility, on-chip Select-RAM memory with edge-triggered and dual-port modes, increased speed, abundant routing resources, and new, sophisticated software to achieve fully automated implementation of complex, high-density, high-performance designs.

Parametrics

XC4005E-4PQ100C absolute maximum ratings: (1)Logic Cells: 466; (2)Max Logic Gates (No RAM): 5,000; (3)Max. RAM Bits (No Logic): 6,272; (4)Typical Gate Range (Logic and RAM): 3,000 - 9,000; (5)CLB Matrix: 14 x 14; (6)Total CLBs: 196; (7)Number of Flip-Flops: 616; (8)Max. User I/O: 112.

Features

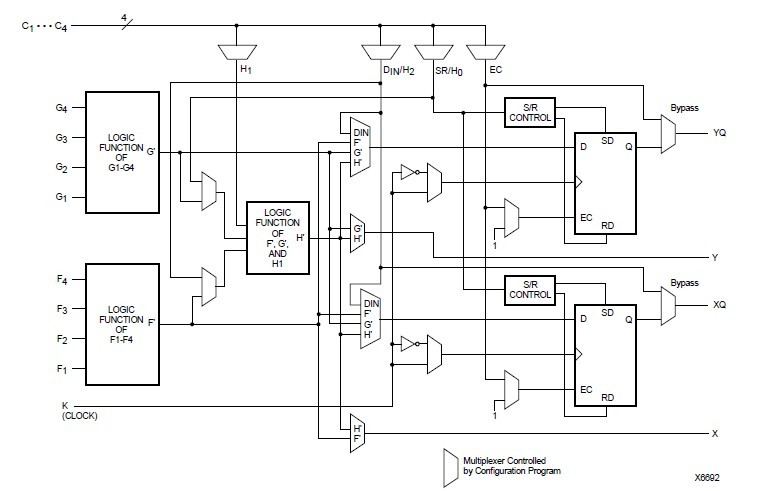

XC4005E-4PQ100C features: (1)System featured Field-Programmable Gate Arrays, Select-RAM memory: on-chip ultra-fast RAM with synchronous write option; dual-port RAM option; Fully PCI compliant (speed grades -2 and faster); Abundant flip-flops; Flexible function generators; Dedicated high-speed carry logic; Wide edge decoders on each edge; Hierarchy of interconnect lines; Internal 3-state bus capability; Eight global low-skew clock or signal distribution networks; (2)System Performance beyond 80 MHz; (3)Flexible Array Architecture; (4)Low Power Segmented Routing Architecture; (5)Systems-Oriented Features, IEEE 1149.1-compatible boundary scan logic support; Individually programmable output slew rate; Programmable input pull-up or pull-down resistors; 12 mA sink current per XC4000E output; (6)Configured by Loading Binary File: Unlimited re-programmability; (7)Read Back Capability: Program verification; Internal node observability; (8)Backward Compatible with XC4000 Devices; (9)Development System runs on most common computer platforms, Interfaces to popular design environments; Fully automatic mapping, placement and routing; Interactive design editor for design optimization Product Specification.

Diagrams

| Image | Part No | Mfg | Description |  |

Pricing (USD) |

Quantity | ||||

|---|---|---|---|---|---|---|---|---|---|---|

|

XC4005E-4PQ100C |

|

IC FPGA C-TEMP 5V 4-SPD 100-PQFP |

Data Sheet |

Negotiable |

|

||||

| Image | Part No | Mfg | Description |  |

Pricing (USD) |

Quantity | ||||

|

XC4000 |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

XC4000A |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

XC4000E |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

XC4000H |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

XC4000X |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

XC4000XL |

Other |

|

Data Sheet |

Negotiable |

|

||||

(Hong Kong)

(Hong Kong)