Product Summary

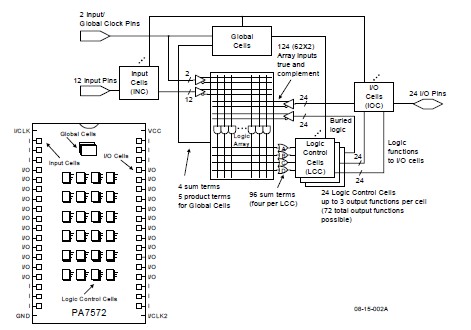

The PA7572P-20 is a Programmable Electrically Erasable Logic (PEEL) Array family based on Anachips CMOS EEPROM technology. PEEL Arrays free designers from the limitations of ordinary PLDs by providing the architectural flexibility and speed needed for todays programmable logic designs. The PA7572P-20 offers a versatile logic array architecture with 24 I/O pins, 14 input pins and 60 registers/latches (24 buried logic cells, 12 input registers/latches, 24 buried I/O registers/latches). Its logic array implements 100 sum-of-products logic functions divided into two groups each serving 12 logic cells.

Parametrics

PA7572P-20 absolute maximum ratings: (1)VCC Supply Voltage Relative to Ground: -0.5 to + 7.0 V; (2)VI, VO Voltage Applied to Any Pin Relative to Ground: -0.5 to VCC + 0.6 V; (3)IO Output Current Per pin (IOL, IOH): ±25 mA; (4)TST Storage Temperature: -65 to + 150 °C; (5)TLT Lead Temperature Soldering 10 seconds: +300 °C; (6)TRVCC VCC Rise Time See: 250 ms.

Features

PA7572P-20 features: (1)24 I/Os, 14 inputs, 60 registers/latches; (2)Up to 72 logic cell output functions; (3)PLA structure with true product-term sharing; (4)Logic functions and registers can be I/O-buried; (5)Up to 3 output functions per logic cell; (6)D,T and JK registers with special features; (7)Independent or global clocks, resets, presets, clock polarity and output enables; (8)Sum-of-products logic for output enables; (9)ICT PLACE Development Software; (10)Fitters for ABEL, CUPL and other software; (11)Programming support by popular third-party programmers.

alt="PA7572P-20 pin connection"

Diagrams

| Image | Part No | Mfg | Description |  |

Pricing (USD) |

Quantity | ||||

|---|---|---|---|---|---|---|---|---|---|---|

|

PA7572P-20 |

Diodes Inc. |

CPLD - Complex Programmable Logic Devices 14 INP 24 I/O 20ns |

Data Sheet |

Negotiable |

|

||||

|

PA7572P-20L |

Diodes Inc. |

CPLD - Complex Programmable Logic Devices 14 Input 24 I/O 20ns |

Data Sheet |

Negotiable |

|

||||

(Hong Kong)

(Hong Kong)